European Journal of Advances in Engineering and Technology, 2020, 7(12):89-92

**Research Article**

ISSN: 2394 - 658X

# High Impact of Low Voltage Controlling SoC Power

# Apoorva Reddy Proddutoori

San Diego Email: apoorvaproddutoori@gmail.com

# ABSTRACT

The scaling of CMOS technology significantly increases the mismatch and fluctuations of transistor threshold voltage, causing bias voltage in SoC designs. A large offset voltage increases clock line jitter and negatively affects dynamic power consumption during reading, detecting the correct speed and operating speed. All MOS transistors used in the low-order dropout (LDO) regulator are low voltage (LV) MOSFETs, saving the manufacturing cost of high voltage devices for the conventional design. Two low voltage transistors are cascaded in the power transmission, creating multiple voltage domains. The main voltage level is used to generate a VDD voltage to the power transistors and as the main error gain to ensure safe operation. The center rail regulator uses stackable transistors to control the high supply voltage. In addition, adaptive biasing is used to achieve good stability and fast transient response. This paper presents a low voltage-based power sense amplifier for offset compensation on integrated CMOS low-order dropout (LDO) with quicker transient response for SoC power management.

Key words: CMOS, power management, low voltage, LDO, transistors, amplifier

# INTRODUCTION

The power controller with multiple integrated controls is widely used in modern portable devices with batteries. These power control systems often use a primary switching controller and multiple downstream controllers. The main switch regulator converts the battery's high DC voltage level (4 V) to low DC voltage (<1 V) with high conversion efficiency (> 92%). Post regulators also produce multiple independent feeds for multiple voltage ranges. A switching regulator inevitably produces a voltage wave in the switching frequency range. The switching frequency of the controller is often in the low frequency range of a few 10-100 kHz to reduce the loss of switching power. Post-regulators should therefore be able to provide good power input rejection to suppress these unwanted low frequency noises. To continue to maintain high power efficiency, minimize impact on target load circuits and reduce cost, these post-regulators must operate at low voltage and low quiescent current (IQ) and achieve fast transient response at low input. variation and minimize their range. The low-order dropout regulator has a simple architecture and fast cycling, which makes it the best candidate to implement these post regulators.

As System-on-Chip (SoC) solutions become more and more popular, integrated power electronics are becoming more popular than individual circuits. To extend the battery life of wearable devices, it is very important to consider the circuit design for the power management system. Therefore, multiple power converters are required. Among them, the low-dropout regulator (LDO) is one of the leading distributed control ICs due to its small size, low power consumption, low cost, low voltage drop, and good output. stability for portable applications, power management systems often require multiple LDO regulators to provide variable supply voltages while minimizing ripple to provide a noise-sensitive block. Therefore, to further reduce voltage costs, it is advisable to implement a fully integrated LDO driver. In general, LDO drivers must handle a wide supply voltage range, for reliability reasons, and require the use of appropriate hardware and structures. The structure of

a conventional LDO driver that relies on high-voltage (HV) MOSFETs to cover the supply voltage range in low-voltage (LV) processes. Therefore, additional structural components are required for HV devices.

A better technique called Adaptive Voltage Scaling (AVS) adjusts the supply voltage dynamically according to variations. However, at a fixed clock frequency but varying voltages, this technique does not consider the intensity of the computation; While some inputs can lead to near zero levels, most inputs can cause a lot of time and thus waste unnecessary energy. The technology adjusts the supply voltage so that the circuit operates correctly at a given constant clock frequency in the face of fluctuations and changing computing load. This allows the designer to make the circuit meet timing constraints without having to consider variations too much, and to automatically adjust the supply voltage during operation at multiple voltage domains.

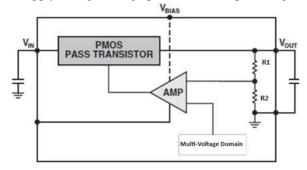

Figure 1: LDO Structure

**AMPLIFIER DESIGN**

#### A. Latch Based

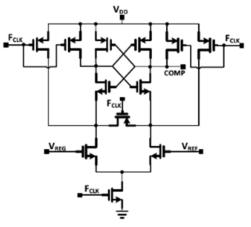

In recent times, latch based LDO implementation has become of wider use due to their low transient response times and low power. Integrating NMOS latch would convert it into a sense amplifier indicating the design to be better suitable for low power circuits.

Figure 2: Latch Based LDO Design

#### **B.** Transient Response Times

The fluctuations and settlement timings during the current transition period is referred to as transient response time. The performance of the circuit mostly depends on the transient response is based on the voltage swings than on the recovery timings, as the voltage swing as small at 20mV can lead to major degradation of the performance of the circuit operating at any load requirements. The transient response is also proportional to the latency of the circuit, faster the response time would lead to low latency, meaning higher performance.

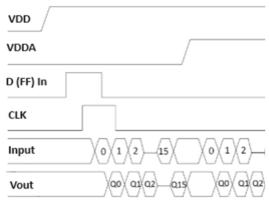

Figure 3: Transient Responses

Furthermore, in order to reduce the voltage fluctuations of the output, the LDO design is modified to incorporate large closed-loop bandwidth and higher exchange rate of current is needed. However, increasing the closed-loop bandwidth can affect the pole/zero locations, and circuits can become too complex, consuming more IQ. TA concept shown in the figure 2, is therefore implemented conditionally to provide additional charge/discharge current paths (rotational current) depending on the state of the output variation detector.

#### **C. Impact of Output Capacitor**

Unbiasedly, the low dropout (LDO) voltage regulator produces an output voltage that is independent of the supply voltage and load current. In above figure 1, an output load capacitance is shown. If we were to reduce the capacitance of this capacitor, including the error amplifier, pass transistor and feedback network. The input transistor implies an input voltage, is proportional to the output voltage linearly, when the range of applied input voltage is sub-low level. The resulting output voltage is detected by an error amplifier and compared with a reference voltage. The error amplifier drives the gate of the emission transistor to the appropriate operating point to obtain the desired output. To compensate for the lack of a large external capacitor, a capacitorless LDO needs an internal fast transition path. The power efficiency of an LDO is directly proportional to the voltage drop (VDO), which is the difference between the input and output voltages.

#### **D. VDD Generation**

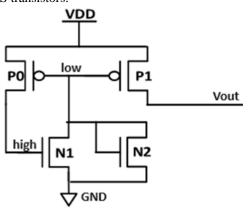

The delayed generation logic for VDD is depicted in Figure 3. The Vout output of this circuit is used to generate the delayed control signal. Before starting, all nodes in the string are at ground (GND) level. When the trigger starts, the supply starts to rise, the low node is connected due to the capacitance P0 and P1. This delays the creep of the high node, which in turn helps the low node stay high. The voltage of the PMOS transistor P0 causes a small delay at the high node. The voltage at the high node is much less than the threshold voltage of the NMOS transistor because the increase slows down the conduction of P1. The low node goes low due to delay, thereby delaying the output supply of Vout. N2 works as a clamp to avoid situations when low node rises higher than the threshold voltage of the PMOS transistors.

Figure 4: VDD Generation Logic

### CIRCUIT SIMULATIONS

To validate the proposed low voltage low power circuits and obtain statistical performance data, we designed and fabricated a validation IP. The latch-based circuit design, each associated with one circuit, can be written in parallel using the D flipflop and CLK pin. This is used to initialize the latch with, which is the opposite of the return value.

The latch outputs can be read sequentially by the mux output Vout. The validation IP has two sources: VDDD for the digital latches and isolated input VDDA for the LDO block. It is important to reset the locks for testing purposes. Since the input to the LDO circuit goes high, we must have 2 inputs, one of which is used to initialize VDDD while VDDA is used to generate the pulse.

Lowering the supply voltage that many causes excessive time swing. A circuit using an NTC must check its own error if it does not lower the frequency too much. Here we describe the bug tracking methods we usually \use, and then the method we use in our technique. *Canary Path* - Critical Path Copy/Trace Technique. The Canary Path technique, or a variation of it, is the most used technique for detecting timing errors. Is a good example of such a technique. A copy of the critical path is usually created with NOT, NOR, or NAND CMOS logic gates. If the critical path and the replica have similar variations, we can estimate the worst-case slow time variations by counting the number of ports the signal passes through in one cycle.

# CONCLUSION

This paper concludes that approaching low-order dropout (LDO) regulators with low output load capacitance adapts an approach dynamically with respect to the input supply voltage varying with the load. This methodology allows us to highlight critical paths with these LDOs for process and temperature variations that dynamically alter the supply voltage by making the modulation frequency constant. Henceforth, the proposed architecture implanting less capacitance LDO balances the input voltage supply as well, not pushing it to as high as 4V.

# REFERENCES

- Jonathan Rosenfeld. Mucahit Kozak, and Eby G. Friedman, "A 0.8 Volt High Performance OTA Using Bulk-Driven MOSFETs for Low Power Mmed-Signal SOCs", IEEE, March 2003

- [2]. Y. Sudha Vani, N. Usha Rani, Ramesh Vaddi, "A Low Voltage Capacitor Based Current Controlled Sense Amplifier for Input Offset Compensation", IEEE, August 2017

- [3]. Shuangxing Zhao, Chenchang Zhan and Guigang Cai, "A 2×VDD-Enabled Fully-Integrated Low-Dropout Regulator with Fast Transient Response", IEEE, May 2017

- [4]. Chung-Hsun Huang, Ying-Ting Ma, and Wei-Chen Liao, "Design of a Low-Voltage Low-Dropout Regulator", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 6, June 2014

- [5]. Harsh Gupta, Gaurav Kumar Mishra, Nidhi, Isma Rizvi, Ajeet Kumar Yadav, "A Capacitor-less Low Drop-out Voltage Regulator for SoC Applications", International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT) – 2016

- [6]. Vivek Nautiyal, Gaurav Singla, Lalit Gupta, Jitendra Dasani, Sagar Dwivedi, Martin Kinkade, "Robust, Self-Timed Power-on Reset Circuit for Low-Voltage Applications", IEEE, May 2017

- [7]. Pierre Nicolas-Nicolaz, Kiyoung Choi, "Dynamic Error Tracking and Supply Voltage Adjustment for Low Power", IEEE, May 2015

- [8]. https://www.analog.com/en/lp/001/fundamentals-of-ldo-design-andapplications.html#:~:text=A%20low%20dropout%20regulator%20(LDO,controlled%20by%20the%20 error%20amplifier.