### Available online www.ejaet.com

European Journal of Advances in Engineering and Technology, 2019, 6(8):67-70

Research Article ISSN: 2394 - 658X

# **Applications of Timing Analysis on Power Optimizations**

## Apoorva Reddy Proddutoori

San Diego apoorvaproddutoori@gmail.com

\_\_\_\_\_

### **ABSTRACT**

This paper presents an entryway delay evaluation methodology that considers dynamic power supply upheaval. We review STA considering static IR-drop assessment and a conventional procedure for dynamic uproar waveform and reveal their cutoff points and issues that start from circuit structures likewise, higher delay antipathy for voltage in state-of-the-art developments. We then, at that point, propose an entrance defer computation that overcomes the issues with iterative computations and considered input voltage drop. Appraisal results with various circuits and upheaval mixture timings show that the proposed technique measures way defer difference well inside 2% error on typical. We work on the capability of static timing assessment exactly when sham ways are considered. The capability of timing examination is fundamental for the display driven smoothing out program since timing assessment is summoned enthusiastically in the internal circle. Regardless, when misdirecting ways are overseen in timing assessment, endless marks need to be made and multiplied, and thus disintegrated the viability. In this paper, we limit the amount of the names through a biclique covering approach, which iteratively takes out a tag if the deceptive way information in the tag is covered by the relationship of various marks. The conveyed marks kill the deceptive way timing and confirmation to cover the certifiable way timings. Since the base biclique covering of the general bipartite chart is NP completed], we use an irrelevant degree mentioning method for managing play out the biclique covering minimization.

Keywords: timings analysis, power, sta, voltage drop, leakage,

#### INTRODUCTION

The circuit scale develops, static timing investigation (STA) turns into a normal way to deal with confirm timing requirements, or rather it is dog recently the best way to perform full-chip timing investigation. In static timing investigation, we engender the most recent appearance time and change time all through a circuit and infer the longest shortest way delays. CMOS circuits comprise of CMOS doors and interconnects, what's more, presently postpone seasons of each part, for example the entryway spread delay and the interconnect proliferation delay, are independently calculated. Concerning interconnect delay, it is notable or then again other comparative strategies can appraise exact progress wave structures proliferating through straight gadget organizations. On the other hand, CMOS doors are non-direct gadgets and the assessment of door delay is intrinsically more confounded. Thusly, delay calculation in light of look-into tables is generally utilized is approach generally requires an earlier portrayal cycle to construct look-into tables utilizing a circuit test system. Because of the constraint of circuit reproduction costs, entryway portrayal is normally performed in two-layered space; yield stacking and progress season of input waveform (slant). The boundary of slant plans to catch the impact of waveform shape on door delay. Recently many elements make progress waveforms more refrain in nanometer advances, for example, crosstalk clamor, between interface inductance and resistive safeguarding, and consequently catching waveform shape by utilizing a solitary boundary of incline is getting harder. By and by, the quantity of boundaries to communicate wave structure shapes doesn't expand on account of entryway portrayal.

The familiar method for approving a circuit is to utilize the known based approach during the static timing examination (STA). The primary disadvantage of such examination lies in its traditionalism. If the subsequent plan edges ensure getting high return values, they might actuate some combination issue during the timing enhancement step. The Factual Static Timing Investigation shows up as a strong choice to lessen these plan edges and furthermore to take entomb and intra-bite the dust process scatterings into account. Anyway, factual techniques can be applied while managing irregular factors, and subsequently can't deal with the deterministic varieties of the temperature (T) and the stockpile voltage (V). This paper handles just the issue of V, T varieties, and all the more definitively their impacts on timings. As previously mentioned, the impacts of V, T minor departure from timings are really taken into account considering the most pessimistic scenario working condition. Concerning process varieties, this can be cynical. For sure, due the intricacy of circuits, temperature and voltage inclinations might be basically as extensive as 50°C and 200mV. To lessen this negativity, techniques should be characterized to make due, during the STA, different working circumstances. In spite of the decrease of plan edges, the meaning of such strategies could be of extraordinary assistance inside the setting of low power applications. For sure, among all the low power plan procedures previously proposed, the utilization of a diminished VDD values or the utilization of various inventory spaces [7-8] are famous arrangements. Anyway these arrangements require serious timing investigation to approve a plan, for example to catch the genuine timing most pessimistic scenario. Taking into account for instance the approval step, this requires describing independently every voltage island with its particular corners. This rapidly prompts think about multiple corners for the approval of double inventory voltage chips.

### TIMING NECESSITY

### A. Timing Modeling

First, Static Timing Examination (STA) not just goes about as an interfacing join among backend and frontend plan exercises, however more critically helps in overcoming any barrier among reenactment and silicon. STA is frequently misjudged to be a mysterious answer for the meet timing prerequisites. While it is without a doubt the obligation of STA specialists to close the timing, it is similarly significant for the register move level (RTL) fashioners to keep away from a few obvious mistakes, which we allude to as structural traps for timing.

In this paper we examine AND-entryway clock gating or potentially door clock gating use cases, some self-evident and some not-really self-evident, which can act as a manual for planners to guarantee that such circumstances are stayed away from forthright in the RTL stage and hence block the emphasis of timing conclusion exercises from, suppose, clock tree blend (CTS) and back to legitimate combination.

We close the paper with a contextual analysis of an odd-recurrence divider circuit that has one execution that yields right outcomes in RTL reproduction and the important changes in the calculation to guarantee that it functions admirably on silicon.

### **B.** Modeling of CMOS Cells

Identify applicable funding agency here. If none, delete this text box.

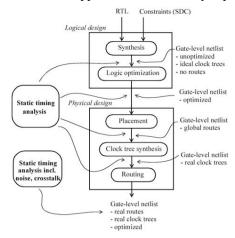

In a CMOSdigital configuration stream, the static timing examination can be performed at a wide range of phases of the execution. Figure 1 shows a run of the flow. STA is seldom finished at the RTL level as, right now, it is more essential to confirm the usefulness of the plan instead of timing. Additionally not all timing data is accessible since the portrayals of the blocks are at the social level. When a plan at the level has been blended to the entryway level, the STA is utilized to check the planning of the plan. STA can likewise be run preceding performing rationale streamlining the objective is to distinguish the most horrendously terrible or basic timing ways. STA can be rerun after rationale improvement to see whether there are bombing ways actually staying that should be advanced, or to distinguish the basic ways.

Towards the beginning of the actual plan, clock trees are considered as great, or at least, they have zero deferral. When the actual plan begins and after clock trees are assembled, STA can be performed to check the timing once more. As a matter of fact, during actual plan, STA can be performed at every single move toward recognize the most horrendously terrible ways. In actual execution, the rationale cells are associated by interconnect metal follows. The parasitic RC (Opposition and Capacitance) of the metal follows influence the sign way defer through these follows. In a run of the mill nanometer plan, the parasitics of the interconnect can represent most of the deferral and power dispersal in the plan.

Accordingly, any investigation of the plan ought to assess the effect of the interconnect on the exhibition qualities (speed, power, and so on.). As referenced beforehand, coupling between signal follows adds to commotion, and the plan check should remember the effect of the clamor for the exhibition. At the consistent plan stage, ideal interconnect might be accepted since there is no actual data connected with the situation; there might be more interest in survey the rationale that adds to the most obviously awful ways. One more method utilized at this stage is to gauge the length of the interconnect utilizing a wireload model. The wireload model gives assessed RC in view of the fanouts of a cell. Before the steering of follows are concluded, the execution instruments utilize a gauge of the directing distance to acquire RC parasitics for the course. Since the directing isn't finished, this stage is known as the worldwide course stage to recognize it from the last course stage. In the worldwide course period of the actual plan, improved on courses are utilized to appraise steering lengths, and the directing assessments are utilized to decide opposition and necessary capacitance to figure wire delays.

Figure 1: CMOS Model Flow

During this stage, one can exclude the impact of coupling. After the nitty gritty directing is finished, genuine RC values acquired from extraction are utilized and the impact of coupling can be investigated. Be that as it may, an actual plan device might in any case utilize approximations to assist with working on run times in processing RC values. An extraction device is utilized to extricate the definite parasitics (RC values) from a steered plan. Such an extractor might have a choice to get parasitics with little runtime and less precise RC values during iterative streamlining and one more choice for definite check during which extremely exact RC values are separated with a bigger runtime.

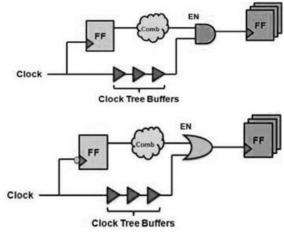

### C. Clock Gating

Clock gating is an indispensable engineering technique to save dynamic power. While the backend devices know about the power scattering, it is in any case a decent plan practice to embed clock gating cells forthright in the RTL. That is on the grounds that inclusion of clock gating cells relies upon the utilization cases and the goal. For instance, in the event that a clock gating either takes care of few flip-tumbles or feeds the clock to a basic IP as would be considered normal to be working more often than not, it's a horrible idea to add clock gating cells.

Figure 2: AND-OR Clock Model

Clock gating cells cause extra unique power and region overheads, and fashioners should know that clock gating cells should possibly be done when the investment funds are supposed to be more than the above. Aside from clock gating cells, now and then straightforward entryways like AND, OR, and NAND can likewise be utilized for clock gating. Yet, these have capricious timing prerequisites, and accordingly it is vital for RTL planners to utilize these cells carefully in the wake of figuring out the timing situations.

### TIMING SYNTHESIS

### A. Waveform Equivalence

One of direct techniques to determine appearance time and incline is the most un-square technique (LSM). Be that as it may, a basic LSM simply approximates the information waveform, and it doesn't think about any data on yield changes. Figure 7 shows a run of the mill inadequate that the basic LSM fizzles. Albeit the result change nearly wraps up before commotion infusion, the LSM determines the approximated waveform that is near the whole real waveform. The central question of identical waveform determination is the way to find a basic district that unequivocally influences the result waveform.

### **B.** Forward Tracing

Imperfections of the regular strategies are made sense of here. The PE (way identification) procedure focuses on ways to work out all way delays, so tremendous, examination time is important. The BO (block arranged) procedure focus to blocks to calculate the most awful postponement, so the delay from a specific beginning stage isn't found. The forward follow procedure of this framework covers these deformities, this procedure depends on the PE method, however, computes the most terrible deferral between the beginning and end focuses by disposing of copied follows to forestall increment of the analysis time which is the deformity of the PE method.

#### **CONCLUSION**

While the timing and commotion examination work really entices of dissecting a plan for timing issues under every possible conceivable circumstance, the best in class actually doesn't permit STA to totally supplant reenactment. This is on the grounds that there are a few parts of timing check that can't yet be totally caught and confirmed in STA.

### REFERENCES

- [1]. B. Lasbouygues, R. Wilson, N. Azemard, P. Maurine, "Temperature and Voltage Aware Timing Analysis Application to Voltage Drops", IEEE, 2007

- [2]. Masanori Hashimoto. Yuji Yamada, Hidetoshi Onodera, "Equivalent Waveform Propagation for Static Timing Analysis", IEEE, 2003

- [3]. Michiaki Muraoka, Hirokazu Iida, Hideyuki Kikuchihara, Michio Murakami, Kazuyuki Hirakawa, "ACTAS: An Accurate Timing Analysis System for VLSI", IEEE, 1985

- [4]. Takaaki Okumura, Fumihiro Minami, Kenji Shimazaki, Kimihiko Kuwada, Masanori Hashimoto, "Gate Delay Estimation in STA under Dynamic Power Supply Noise", IEEE, 2010

- [5]. https://www.synopsys.com/glossary/what-is-static-timing-analysis.html

- [6]. https://www.vlsi-expert.com/2011/02/timing-analysis-basis-what-and-why.html

- [7]. https://www.embedded.com/static-timing-analysis-bridging-the-gap-between-simulation-and-silicon/

- [8]. J. Bhasker, Rakesh Chadha, "Static Timing Analysis for Nanometer Designs a Practical Approach", ISBN, 2009