European Journal of Advances in Engineering and Technology, 2023,10(5):84-87

**Research Article**

ISSN: 2394-658X

# **Dynamic Power Suppression with SoC Clock-Skew Resonance**

## Apoorva Reddy Proddutoori

San Diego Email id – apoorvaproddutoori@gmail.com

### ABSTRACT

The issue of assembly the skew imperative in clock trees gets to be much difficult as the IC plan worldview has been moving to different control supply mode plan, in which the clock skew changes powerfully concurring to the voltage levels of the connected control modes amid the execution. Clock slant minimization is a significant subject in the plan of simultaneous consecutive circuit. As the cycle innovation scaling, the impact of cycle/voltage/temperature (PVT) minor departure from clock slant has turned into a serious concern. In this paper, we propose a self-changing component that can powerfully designs the deferrals of ADBs to diminish the impact of PVT minor departure from clock slant. As a cure to bargain with the clock skew optimization issue of the plans with different control modes, which are presently a standard for more control plans, numerous investigates have centered on the utilization of movable delay buffers (ADBs), whose delay can be balanced powerfully, and endeavored to supplant the least number of clock tree buffers with ADBs. In any case, none of the works have considered the nearby clock skew necessities in clock trees, and the clock trees are optimized critically, coming about in overabundance ADB addition. In this work, we propose an arrangement to the issue of ADB inclusion to resolve the contrast of neighborhood clock skews in clock trees.

Key words: power, clock, delay buffers, PVT, clock tree

## INTRODUCTION

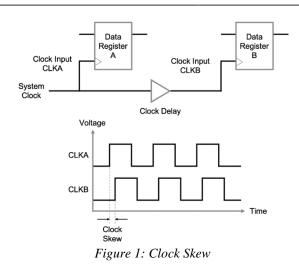

The progression in chip planning handle has been quick. The recurrence of operation has continuously been on rise. With increment in complexity level of the circuits, it is imperative to note that not each component within the circuit encounters the same clock timings. This leads to diminished productivity and in cases misfortune of information. The three enormous concerns for the coordinates circuits plans are the clock skew, constriction and control misfortune.

Clock slant and power dispersal are two primary worries for clock tree blend. Since clock slant affects the greatest clock recurrence, there is an interest to limit the clock slant. Also, since the clock tree is the biggest wellspring of force dispersal, decreasing the power utilization of clock tree is likewise a urgent issue. Clock gating has been perceived as quite possibly of the most successful strategies to lessen the clock power utilization (i.e., the dynamic power utilization of the clock tree). Routinely, a gated clock tree is much of the time addressed by an action driven clock tree.

The request for tall productivity clock buffer and inverters increments as the number of transistors coordinates on a chip increment. Clock flag are an indispensably portion of each circuit. Clock signals are utilized for timing and deciding when a useful piece will work. Both these operations ought to be performed at precisely their designated times to guarantee that the preparing of information takes in a step-by-step way. Clock flag guarantees that steady yield is accomplished within the past step some time recently continuing to the another preparing arrange, without productive timing signals nonsense values can be engendered and lead to incorrect yields.

In an action driven clock tree, the clock control rationale (i.e., the empower signal) is alluded to as an action design, which is a string comprised by 0's and 1's, showing the clock signal is handicapped or empowered in a specific cycle, individually. Many exploration endeavors have been paid to the low-power action driven clock tree combination issue.

The essential thought of these methodologies is to blend the hubs with comparable action example to impair the clock signal as could really be expected. With numerous components requiring the source clock, the diverse components get the input clock source at distinctive occurrence of time, in this way coming about in a wonders called clock skew. With tall skew the circuit works at decreased effectiveness. This makes clock skew a major issue for the architects to overcome. Expansive circuits have correspondingly huge fan-out which leads to delay within the proliferation.

Figure 2: Clock Tree Network

The delay distinction needs to be diminished to guarantee usefulness of any planned circuit. Edge activated components in a circuit require moment edge transmission for moment exchanging, this may be guaranteed by having little rise and drop times for the clock flag.

#### 1. CTS DESIGN

The proposed plan procedure incorporates three fundamental stages. To start with, we develop the geography of gated clock tree. Then, we add sham cells for load adjusting. At long last, we perform gated clock tree steering. In the accompanying, we depict these three stages, separately.

#### A. Numerous Buffers

Various source supports are placed on the chip with a clock source. The clock signal is shipped off each chip through vertical lines from the cushions. The upward lines (for example TSVs, on-chip vertical interconnects, and knocks) to each chip are isolated. By expecting there will be a ton of stacked contributes the future, we likewise propose a strategy including grouping some chips associated with vertical TSVs, which can decrease the number of clock source cradles and TSVs representing an instance of bunching two chips.

#### B. Resonance

Typically, the local clock sections are the buffered signals that feed the registers, as shown in fig. 2, this is a square (wave) clock. Inserting l eliminates power harvesting since CDN capacity is in its leaves, 's advantage will come from expanding 's flip-flops. The clock allows clock power to resonate between local clock capacities.

Figure 3: Clock Distribution Layout

#### C. Tuning

The symmetric inverter has more draw up and pull-down strength then the overall CMOS Inverter coming about in speedier advances in the high-low edges of the clock. The symmetric inverter is adjusted to be made tunable. The semiconductors involve the tunable network which gives shifting deferral as required.

#### 2. CLOCK NETWORK PARAMS

After the geography of gated clock tree (movement driven clock tree) is developed, the result capacitance of every cell is unique. To lessen clock slant, we add sham cells to adjust the result capacitance of every cell at the cell level. For instance, the yield capacitance of cell V5 and the result capacitance of cell V6 are unique, since cell V5 drive two AND entryways and cell V6 drive one AND door and one cushion entryway. Thusly, we might have to add faker support D1 as displayed to expand the result capacitance of cell V6 for load adjusting. Then, at that point, we play out the tree directing in the base up way. We utilize the RC models address the same circuits of an interconnect wire, a cushion and a clock door gives a wire and gives the same circuit, in which Co means the wire capacitance what's more, L signifies the wire length give a cradle entryway and an AND door, separately gives the same circuit of cradle endlessly door), (in which Cg signifies the info capacitance, Dg signifies the inborn postponement, and Rg indicates the driver obstruction. As per the same circuit, we can utilize Elmore defer model to find zero slant blending point by utilizing concurrent conditions. Note that the minimization of the steering length compares to the minimization of the non-familiar way length.

- A. Clock Slew: The time that a given flag takes to rise from a level of 10% of the rail voltage to the level of 90% of the rail voltage is alluded to as rise slew. Essentially, the time that a given flag takes to drop from a level of 90% of the rail voltage to the level of 10% of the rail voltage is alluded to as drop slew. Clock slew straightforwardly impacts the inside or the short-circuit control scattered inside the clock organize, which is scattered when current streams straightforwardly from the supply into the ground when both Quip (Pull-Up Arrange) and PDN (Pull-Down Arrange) are on. More honed (numerically lower) slews cruel Quip and PDN are at the same time on for a shorter length, subsequently lower inside control. One might contend that they can utilize huge clock drivers to guarantee more honed moves. But this will come at the fetched of zone (thus spillage control) conjointly the exchanging control.

- **B.** Least Beat Width: All sequential components within the plan- that incorporates registers, locks and recollections have a least beat width prerequisite for the clock flag. The min beat width necessity is fundamental to meet to permit circuitry inside to a enlist, lock of an SRAM to total their operations some time recently being able to capture a modern information or make the information accessible at their yield pins in a dependable way. This prerequisite for the beat width may exist within the frame of tall beat width and moo pulse width or too within the shape of least clock period.

- **C. Cycle Check:** Let's to begin with attempt to get it what causes an obligation cycle of the clock flag to be mutilated. Unequal rise and drop times of the clock repeaters is the essential cause of obligation cycle mutilation. Originators have the choice between buffers and inverters to construct the clock tree. Buffers are nothing but back-to-back inverters, with the primary inverter being small because it drives a littler separate as it were to another inverter. The moment inverter is planned to be bigger since it ought to drive a long wire comprising of the RC arrange and/or a huge fan-out. This asymmetry causes the rise and the drop edges to be skewed and depending on the number of repeater stages between the clock source and the clock sink, this distinction builds up. This can be the essential reasons why originators lean toward to utilize inverters or perhaps symmetrical clock buffers to construct the clock tree.

- **D.** Clock Power: Clock control is ordinarily a major component of the in general dynamic power scattered within the design. The truth that clock flag regularly has the most noteworthy recurrence within the plan is

one reason why architects ought to be careful of the clock control. Physical plan engineers have very a couple of strategies at their transfer to undertake and diminish the generally clock control.

**E. Clock Gating:** By switching off the clock to the registers that are inactive, planners can save the inside power scattered inside the registers. Clock Gating cell (additionally generally alluded to as incorporated clock gating cell or ICG) are utilized for this reason. Clock gating can be coarse grained and fine grained. Coarse grained clock gating is generally still up in the air at the engineering level, where one clock door might go off the clock to a whole module. Fine grained clock gating controls when to close the clock to a little bundle of registers like a tiny sub-module or a transport inside a greater module. Furthermore, it's additionally considered normal to have transitional degrees of clock gating too.

#### **3. CONCLUSION**

A clock circulation network with various source supports (MSB CDN) was introduced. The supports for communicating a clock sign to each chip were on a chip with a clock source. Each chip gets the sign with recipients that were something similar size. The deferral and slew were chosen as per the cradles and collectors. Consequently, the upward clock slant can be decreased. This strategy enjoys the benefit that every one of the chips with the exception of the clock source chip can perform clock appropriation plan, which is equivalent to single chip plan strategies such as the most well-known cushioned clock tree union (CTS). To manage many stacked chips, a bunching technique was moreover introduced. The investigation expecting 10 nm innovation showed that the proposed technique is powerful for slant decrease.

#### **4. FUTURE WORKS**

This ETL and Automation system prototype can be used alongside the machine learning algorithm for algorithmic trading for a better data pipeline for analysis. As data volumes grow, the scalability and performance of our ETL system become crucial. Future research could explore techniques for handling larger datasets efficiently, potentially utilizing parallel/distributed computing or cloud-based solutions. While we have mentioned the potential use of different techniques for data processing, future work could delve deeper usage of AutoETL. [6]

#### REFERENCES

- Ignatius Bezzam and Shoba Krishnan, "Minimizing Power and Skew in VLSI-SoC Clocking With Pulsed Resonance Driven De-skewing Latches", 27th International Conference on VLSI Design and 2014 13th International Conference on Embedded Systems, 2014

- [2]. Tsung-Tang Lin, Wen-Pin Tu, Shih-Hsu Huang, "Self-Adjusting Mechanism to Dynamically Suppress the Effect of PVT Variations on Clock Skew", IEEE, April 2014

- [3]. Nanako Niioka, Masashi Imai, Masa-aki Fukase, Yuuki Miura, Kaoru Furumi, and Atsushi Kurokawa, "Clock Skew Reduction for Stacked Chips Using Multiple Source Buffers", 15th International Symposium on Communications and Information Technologies (ISCIT), 2015

- [4]. Deokjin Joo, Taewhan Kim, "Managing Clock Skews in Clock Trees with Local Clock Skew Requirements Using Adjustable Delay Buffers", IEEE, Sept 2015

- [5]. K.R. Radhakrishnan\*, S. Subha Rani, "Clock skew optimized VLSI Architecture for Zero Frequency Filter", International Conference on VLSI Systems, Architectures, Technology and Applications (VLSI-SATA), 2016

- [6]. Ravi S, Suyash Trehan, Mohit Jain, Harish M. Kittur, "High Performance Clock Path elements for Clock skew reduction", 2nd International Conference on Intelligent Computing, Instrumentation and Control Technologies, 2019